By: Atul Prasad Deb Nath and Kshitij Raj

Stage: Intermediate

Summary

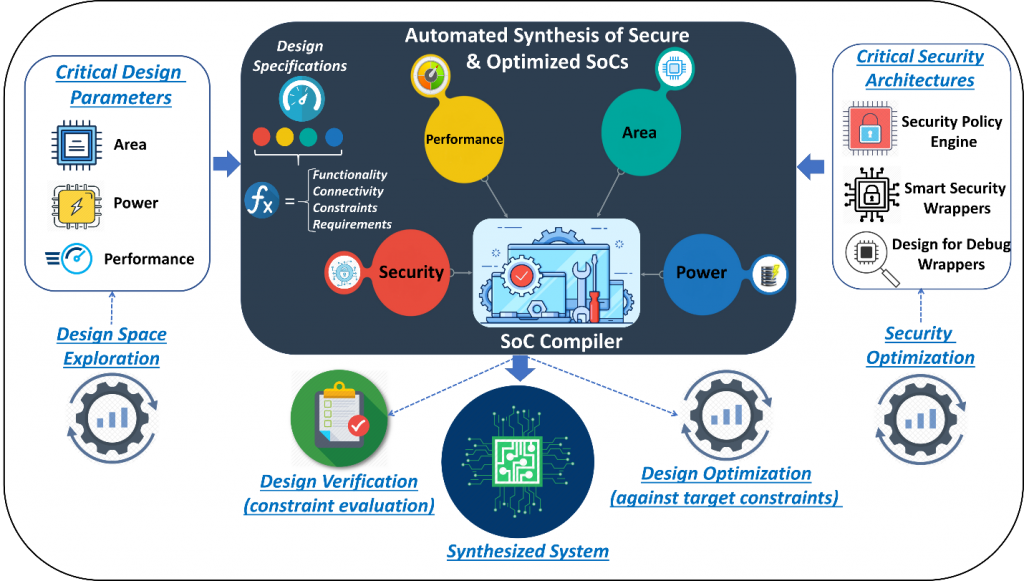

This a novel CAD framework and EDA tool, namely secure SoC Compiler aka SoCCom, for automated synthesis of secure and optimized System-on-Chip (SoC) architectures. The developed technology streamlines the integration of security features into existing design flow while enabling automatic IP integration and design optimization through a configurable tool-flow-methodology (TFM). The TFM enables the generation of a wide variety of secure and optimized SoC designs by:

- Automating the process of IP integration and allowing configurable assembly of complex, scalable systems

- Enabling systematic integration of security features to generated SoCs and ensuring system trustworthiness via correct by construction security architectures

- Facilitating the evaluation and optimization of generated designs in terms of critical system parameters ie, power, area, performance, and security.

Contact

Input/Output Interface

- Input: JSON file describing the SoC components and security requirements

- Output: Synthesizable Verilog and SystemVerilog RTL

Dependencies

- Design tools for FPGAs: Xilinx Vivado / Altera Quartus

- Design tools for ASICs: Design Compiler

- Scripting: Python 3.6, Bash, TCL support.

Licensing

Proprietary, Undergoing patent filing process