By: Muhammad Arsath K F (IIT Madras), Vinod Ganesan (IIT Madras), Rahul Bodduna (IIT Madras), and Chester Rebeiro (IIT Madras)

Stage: RTL, HDL, Gate-Level

Summary

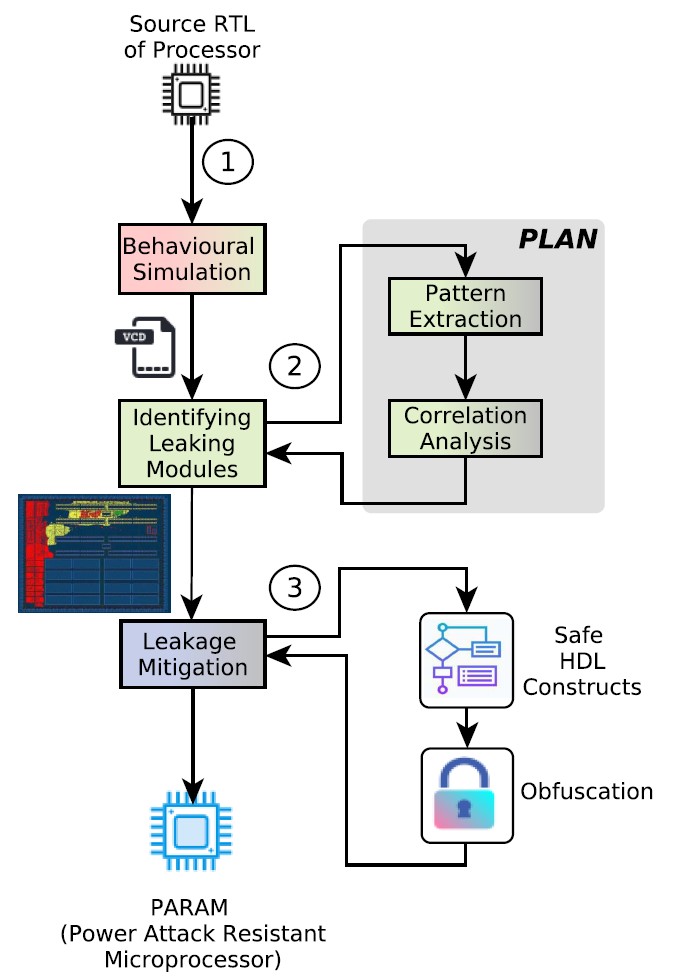

- PLAN (Power attack Leakage ANalyzer) performs power side-channel analysis of digital circuit designs at the RTL or gate-level netlist stage.

- PLAN performs a large number of behavioral simulations on the input design and collects the corresponding traces for a certain reference / oracle signal in the design, as well as the other signals in the design. Then, it applies statistical metrics on the collected traces to compute the correlation between each signal and the reference signal, which gives an estimate of the leakage score of each signal.

- PLAN can be used for an early estimation of power side-channel vulnerability. However, for the correlation analysis to provide a reasonably accurate estimate of the leakage scores, a large number of simulations are required.

Contact

Input/Output Interface

- Input: Hardware design provided in RTL / Gate-level netlist (Verilog); A reference signal in the design

- Output: A list of leakage scores for each signal in the design

Dependencies

Python 3, certain Python modules (tqdm, pyverilog, z3-solver, numpy, scipy, Verilog_VCD, pandas, matplotlib)

Licensing Info

BSD 3-Clause License Copyright (c) 2012-2020, IIT-Madras All rights reserved.

References

PARAM: A Microprocessor Hardened for Power Side-Channel Attack Resistance Journal Article

In: 2020 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), 2020.